LDPC NAND Codec IP Core: 2KB, 0.90 Rate

The IP core implements Boyuan’s NAND Flash LDPC (18176, 16384) algorithm. The code belongs to irregular QC LDPC codes and has large girth 8. The LDPC NAND Codec IP core are highly configurable. The IP user can configure the IP Core to meet their NAND Flash system design trade-offs among the BER performance, the I/O throughput and the implementation complexity.

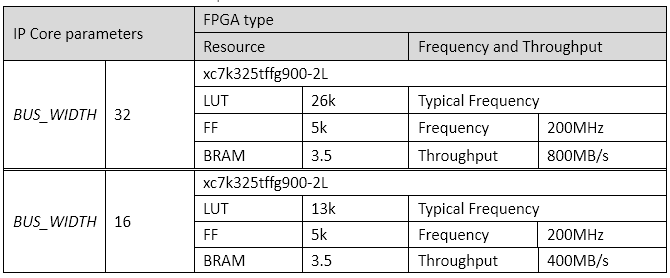

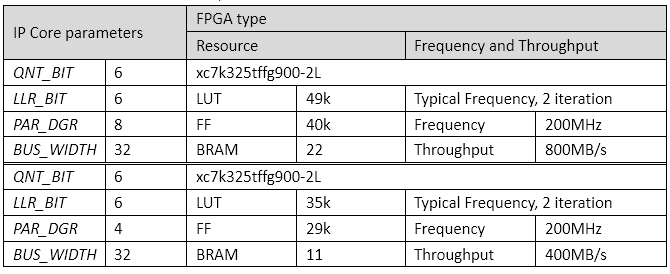

Impletation

Applications

The core can be utilized in the controller of a variety of NAND Flash including:

- TLC NAND Flash

- Novel 3D NAND Flash

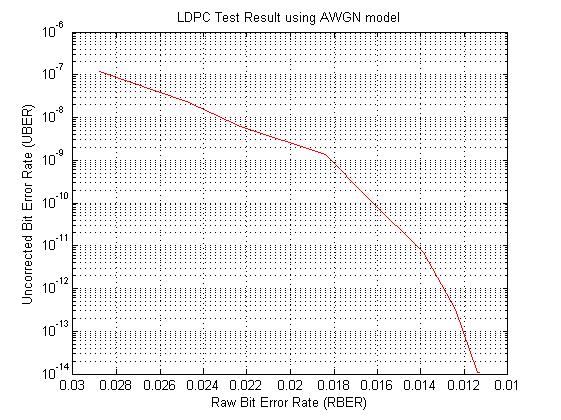

Test Result using FPGA

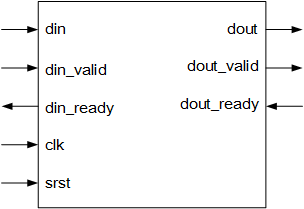

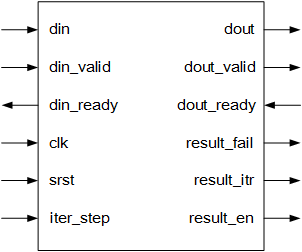

Port Map

Encoder Port Map:

Decoder Port Map:

Block Diagram

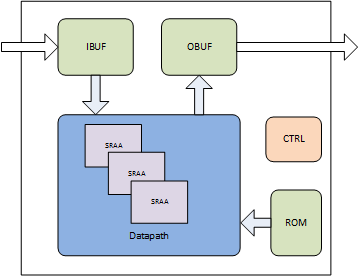

Encoder Block Diagram:

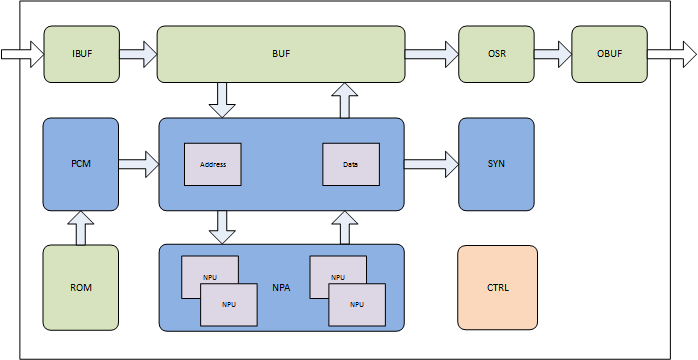

Decoder Block Diagram:

Features

- Synchronoused design

- Parameterized input data width

- Parameterized output data width

- Parameterized internal LLR symbol width

- Early decoding iteration stop detection unit

- Parameterized number of node process unit

- Dynamic scale factor for Min-Sum decoding

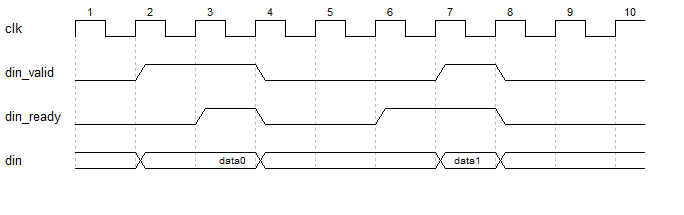

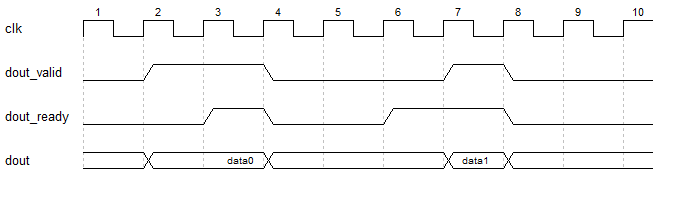

Standard Interface Timing

- valid/ready data transfer protocol

- data source set/clear valid

- data destination set/clear ready

Downloads (PDF)

Related Products

Sales E-mail: sale@bjbytech.com

Technical consult E-mail: tech@bjbytech.com

Cell Phone: +8613601005061

Support

The core as delivered is warranted against defects for three months from purchase. Free remote technical support is provided for twelve months, includes consultation via phone and E-mail. The maximum time for processing a request for technical support is three business days.

Verification

The core has been verified through extensive simulation and rigorous code coverage measurements.

Deliverables

The core is available in RTL source code (Verilog) and FPGA (Netlist) forms, and includes everything required for successful implementation:

- RTL source code or post-synthesis EDIF Netlist (FPGAs)

- Wrapper for pin compatible replacement

- Testbench (self-checking)

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications