LDPC编解码器IP核 (NAND Flash)

IP核实现博原科技的针对大容量、低可靠性的NAND型闪存的LDPC(18176, 16384)算法,码字数据位长度2KB(或16384 bit),码率0.9014。该码属于非规则准循环低密度校验码,设计围长为8。编解码器IP核提供多种可配置的参数,以满足不同系统在BER性能,I/O吞吐量和实现复杂度的折中。

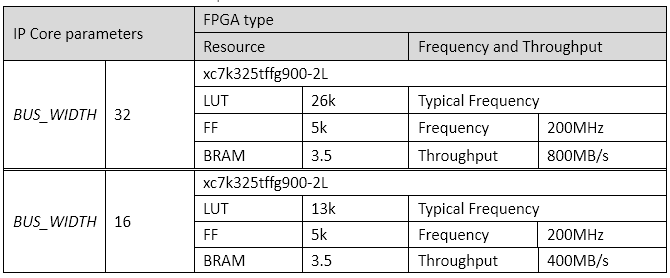

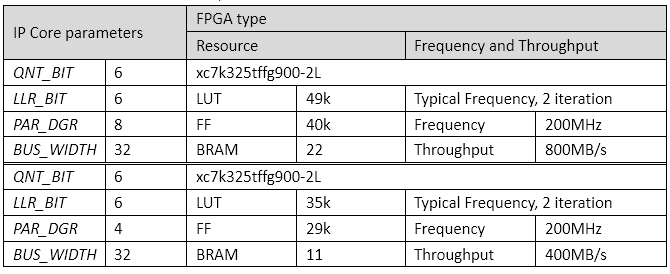

综合结果

应用范围

LDPC编解码器IP核可用在以下系列的NAND Flash的纠错码中:

- TLC NAND Flash

- 新型的3D NAND Flash

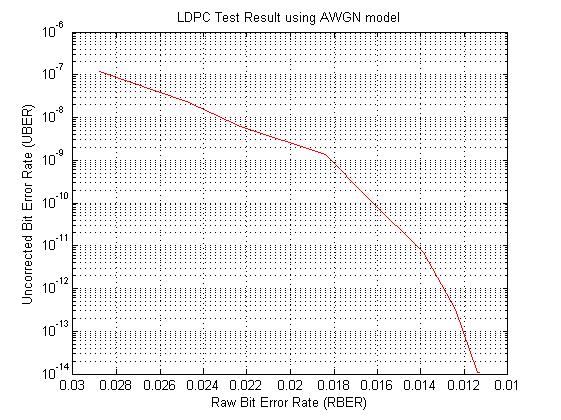

FPGA性能测试结果

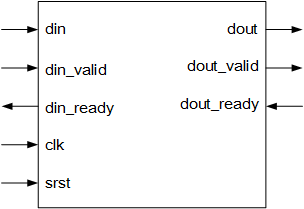

端口映射

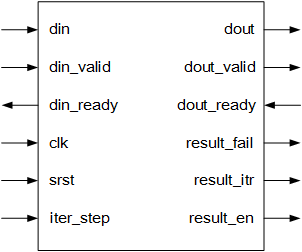

编码器端口映射:

解码器端口映射:

结构示意图

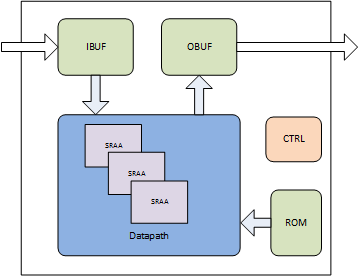

编码器结构示意图:

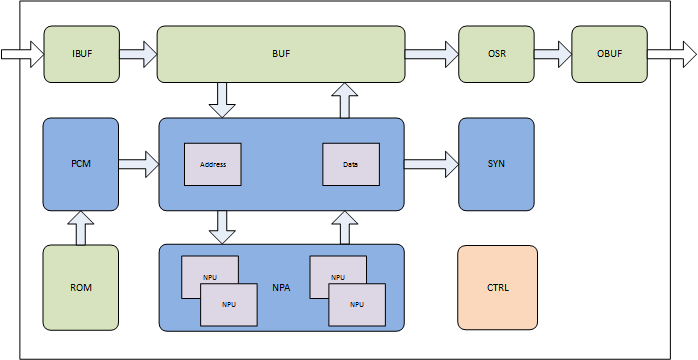

解码器结构示意图:

技术特征

- 全同步设计

- 参数化的输入数据位宽

- 参数化的输出数据位宽

- 参数化的内部LLR数据位宽

- 解码迭代提前终止逻辑模块

- 参数化的节点处理单元

- 动态的最小和译码算法的收缩因子

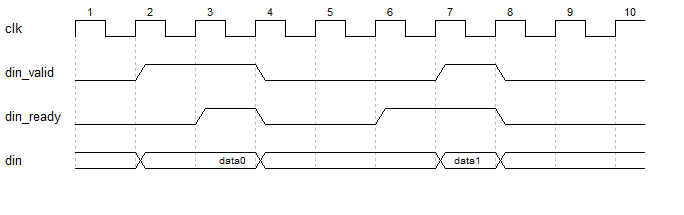

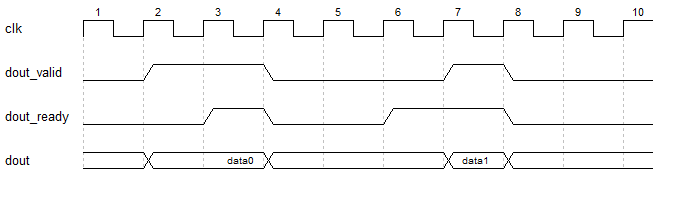

标准的接口协议

- valid/ready数据传输协议

- 数据发送端复位/置位valid信号

- 数据接受端复位/置位ready信号

技术支持

从交货日起提供为期12个月的免费技术支持,包括电话咨询和电子邮件咨询。技术问题响应时间不超过三个工作日。

功能及时序验证

IP核在发布前,已经通过了大量的仿真,以及必要的FPGA验证。

授权内容

IP核提供2种可选的授权方式:RTL源代码(Verilog)或FPGA网表(EDIF),以及其他必要的技术文件:

- RTL源代码(Verilog)或FPGA网表(EDIF)

- 顶层PIN兼容的包文件

- 完整的仿真或测试平台

- 测试矢量,对比数据等用于仿真测试的数据

- 综合脚本

- 用户手册,使用说明等技术文档