NAND Flash Controller with BCH Codec

NAND Flash memories provide higher storage volumes with lower price compared to NOR Flash memories. However, the much more sophisticated control and management are required for NAND Flash due to their “page” organized array structure and lower reliability.

Boyuan NAND Flash Controller (NFC) with BCH Codec IP Core provides a Register Transfer Level (RTL) solution for the SLC/MLC NAND Flash memories. The Core guarantees the industry reliably for NAND Flash applications and provides standard interface that easies the integration. The integrated higher performance BCH core guarantees the high reliability with the steady high read and write throughput from the early to the End-Of-Life (EOF) of NAND Flash memories.

Impletation

Applications

The controller core can be utilized to control a variety of NAND Flash including:

- SLC NAND Flash

- MLC/eMLC NAND Flash

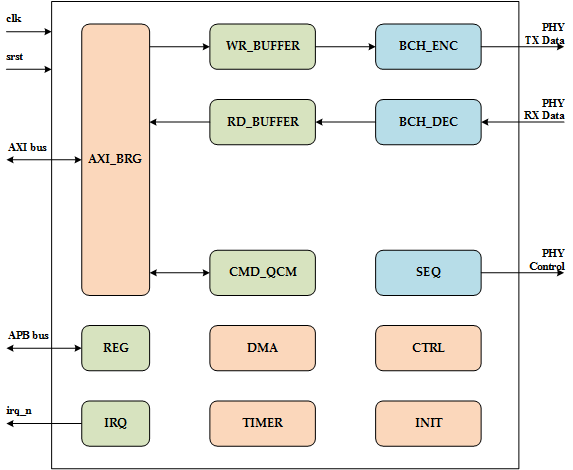

Block Diagram

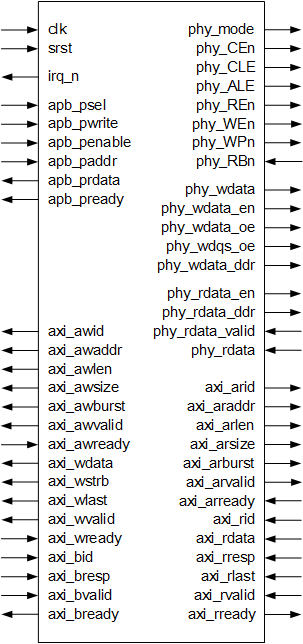

Port Map

Features

- Compliant to ONFI 2/3/4

- Supports 8-bit NAND Flash interface

- Supported Page size: 2KB, 4KB, 8KB and 16KB

- Supported Admin Commands: Reset, Read ID, Read status, Set/Get Feature

- Supported I/O Commands: Read Parameter and Unique ID, Page Read and Program, Block Erase

- Provides Admin & I/O command Queue

- High performance BCH Codec: 1kB data block and configuration ECC level

- Simplified NAND Flash Controller PHY interface

Standard Interface

Downloads (PDF)

Related Products

Sales E-mail: sale@bjbytech.com

Technical consult E-mail: tech@bjbytech.com

Cell Phone: +8613601005061

Support

The core as delivered is warranted against defects for three months from purchase. Free remote technical support is provided for twelve months, includes consultation via phone and E-mail. The maximum time for processing a request for technical support is three business days.

Verification

The core has been verified through extensive simulation and rigorous code coverage measurements.

Deliverables

The core is available in RTL source code (Verilog) and FPGA (Netlist) forms, and includes everything required for successful implementation:

- RTL source code or post-synthesis EDIF Netlist (FPGAs)

- Wrapper for pin compatible replacement

- Testbench (self-checking)

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications