BCH HINOC2.0 Codec IP Core

The BCH IP core for HINOC2.0 implements BCH algorithm in HINIOC 2.0 protocol. The BCH encoder generates parity bits and the BCH decoder finds & corrects error bits using three sub-modules: Error Detect Coder (EDC), Key Equation Solver (KES) and Chien Search Machine (CSM). These sub-modules are scheduled in a pipeline manner, which mean the BCH decoder can decode three data frames concurrently with each frame in each decoding stage. The KES module is optimized to get equivalent latency with other sub-modules. The CSM is implemented area efficiently using BOYUAN’s proprietary technologies. Both the BCH encoder and decoder is optimized for more than 1Gpbs throughput communication in ASIC implementation.

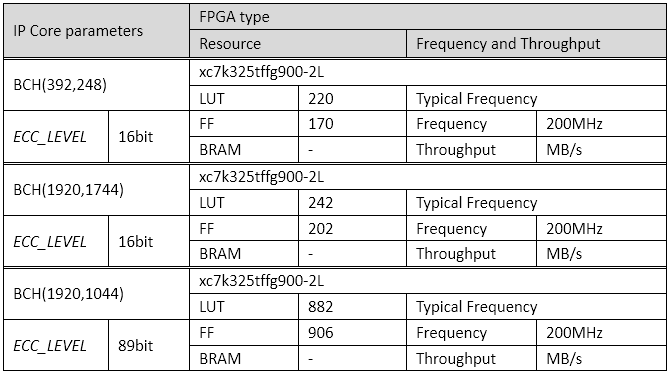

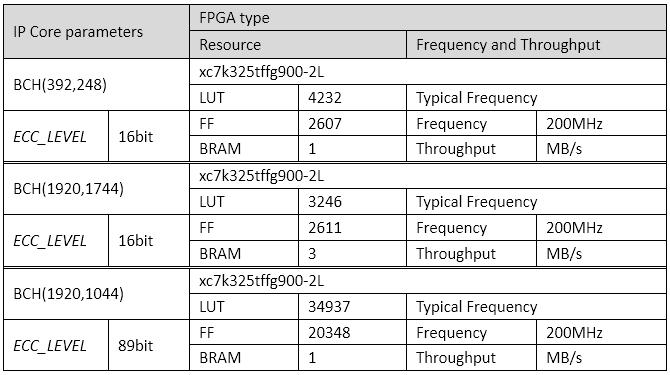

Impletation

Applications

The core can be utilized in the controller of a variety of NAND Flash including:

- HINOC2.0 FEC

Parity Length

| BCH(392,248) | BCH(1920,1744) | BCH(1920,1044) | |

|---|---|---|---|

| ECC Level | 16bit | 16bit | 89bit |

| Parity Length | 18B | 22B | 876bit |

Port Map

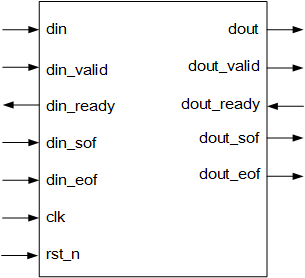

Encoder Port Map:

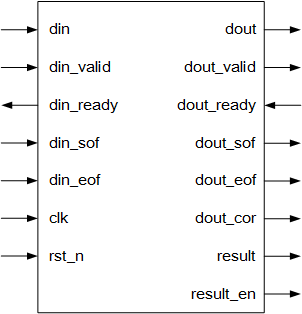

Decoder Port Map:

Block Diagram

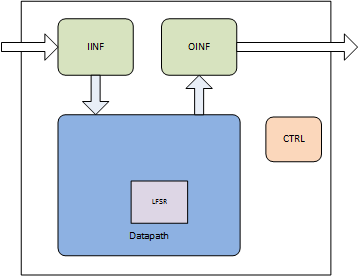

Encoder Block Diagram:

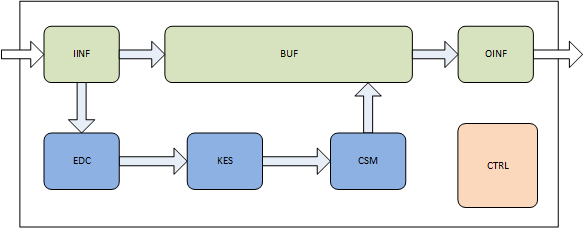

Decoder Block Diagram:

Features

- Synchronoused design

- Supported BCH algorithm: BCH(392,248), BCH(1920,1744) and BCH(1920,1044)

- Parameterized input data width

- Parameterized output data width

- Full pipelined decoder

- Report decoding results

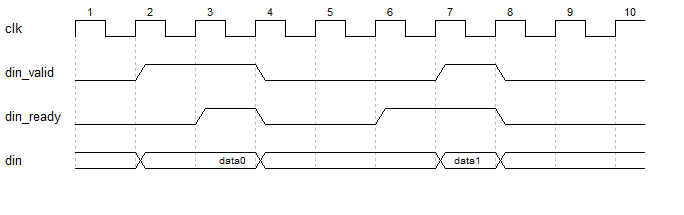

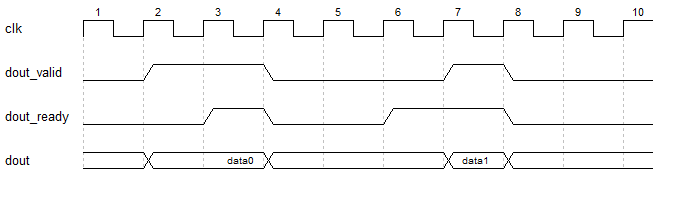

Standard Interface Timing

- valid/ready data transfer protocol

- data source set/clear valid

- data destination set/clear ready

Downloads (PDF)

Related Products

Sales E-mail: sale@bjbytech.com

Technical consult E-mail: tech@bjbytech.com

Cell Phone: +8613601005061

Support

The core as delivered is warranted against defects for three months from purchase. Free remote technical support is provided for twelve months, includes consultation via phone and E-mail. The maximum time for processing a request for technical support is three business days.

Verification

The core has been verified through extensive simulation and rigorous code coverage measurements.

Deliverables

The core is available in RTL source code (Verilog) and FPGA (Netlist) forms, and includes everything required for successful implementation:

- RTL source code or post-synthesis EDIF Netlist (FPGAs)

- Wrapper for pin compatible replacement

- Testbench (self-checking)

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications