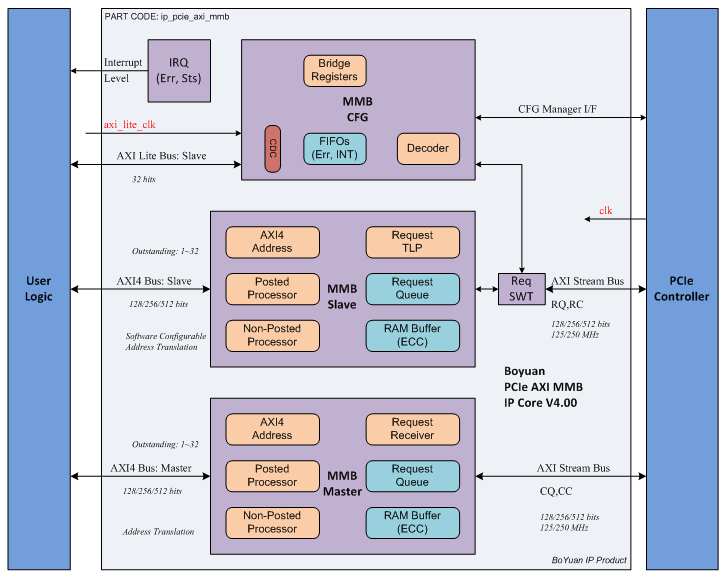

PCIe AXI Memory Mapped Bridge - AXI内存映射桥

北京博原科技的PCIe AXI Memory Mapped Bridge IP(简称PCIe MMB),构建AXI Stream接口类型的PCIe控制器与用户逻辑/内存之间的桥梁,实现AXI Stream与AXI4总线之间的双向转换,同时通过扩展的VSEC配置空间,支持灵活的地址映射。RP模式下,支持ECAM功能,用户逻辑可通过AXI Lite总线实现对PCIe链路本地和对端设备的配置空间的访问。采用AMBA标准总线,极大得简化了PCIe应用层的开发,是用户易于在SOC环境中集成和使用PCIe控制器。

关键特征:

- v3.0支持Xilinx v7系列PCIe 3.0硬核

- v3.0u支持Xilinx ultra系列PCIe 3.0硬核

- v3.1支持博原科技PCIe软核v3.10

- v4.0v支持Xilinx versal系列PCIe 4.0硬核

- 数据位宽:128/256

- 支持Root Port/Endpoint Point(EP)模式

- 支持PCIe用户自定义扩展配置空间VSEC

- 支持单PF:Function Number可配置

- 支持AXI Lite总线从接口:用户逻辑直接访问本地配置空间。RP模式下,支持ECAM配置访问方式,即通过设置BDF Number访问PCIe链路对端设备配置空间

- 支持AXI Master总线主接口:PCIe链路对端设备访问本地内存空间。地址转换可配置,访问最大线程数可配置,猝发读写最大长度可配置

- 支持AXI Master总线从接口:本地访问PCIe链路对端设备内存空间。地址转换可配置,访问最大线程数可配置,猝发读写最大长度可配置

- 兼容AMBA AXI4协议标准:支持非对齐地址传输,支持Narrow Burst,支持INCR的突发类型

- 可配置的最大负载大小(MPS)和最大读请求大小(MRRS):128 ~1024 bytes。MPS/MRRS分别对应AXI写和AXI读Burst长度

- AXI读支持乱序返回和交织返回

- 支持传统中断、MSI中断接收

- 支持异常检测和中断汇报

- 支持消息接收

- 支持ECC RAM

- 支持AXI和PCIe Cache类型转换

- 双时钟设计:寄存器接/内部逻辑时钟

应用范围

PCIe AXI MMB IP,与AXI Stream接口的PCIe Controller IP集成使用,为应用提供标准的AXI4和AXI Lite总线的PCIe控制器方案,可以广泛应用于以下应用场景:

- PCIe跟设备类(RP):例如NVMe Host Controller,NVMe Host Accelerater

- PCIe端设备类(EP):例如NVMe Target Accelerater,Smart NOC,AI Accelerater

结构示意图

实现示例 A: Xilinx "xcvm1402-vsvd1760-2MP-e-S"

PCIe AXI MMB IP采用以下配置参数:

- 功能:RP

- 位宽:256 bit

- 最大读请求:512 Byte

- 最大读请求:512 Byte

- Narrow Burst:开启

- AXI从接口最大传输线程:8

- AXI主接口最大传输线程:64

- AXI BAR至PCIe BAR地址转换:开启

- PCIe BAR至AXI BAR地址转换:关闭

Resource |

Estimation |

Available |

Utilization % |

|---|---|---|---|

LUT |

10422 |

565760 |

1.84 |

LUT RAM |

118 |

282880 |

0.04 |

FF |

20907 |

1131520 |

1.85 |

BRAM |

23 |

1150 |

2.00 |

注:综合策略采用“Vivado Synthesis Defaults”。

总线/接口

- AXI Stream总线:PCIe数据流

- AXI Lite总线从接口

- AXI4总线主接口

- AXI4总线从接口

- VSEC:用户自定义扩展配置结构体

- ECAM:扩展的配置空间

协议

技术支持

从交货日起提供为期6个工作月的免费技术支持,包括电话咨询和电子邮件咨询。技术问题响应时间不超过三个工作日。

功能及时序验证

IP核在发布前,已经通过了大量的仿真,以及必要的FPGA验证。

授权内容

IP核授权方式和技术文件:

- FPGA网表(EDIF)

- 完整的仿真或测试平台

- 综合脚本

- 用户手册,测试报告等技术文档

- 软件驱动,测试例程

- FPGA工程示例

评估/购买:

- : sale@bjbytech.com

- : +86-13601005061