NVMe Target IP Core

Compared to traditional SCSI protocol, NVM Express has much lower data transfer latency and much higher efficiency, which is more suitable for the current multi-core CPU architecture and the high IOPS requirement application. The Boyuan NVMe Target core provides a hardware accelerated queue management interface for NVMe commands and completions. The core is an industry standard NVMe device target controller IP core that allows customers to build high performance NVMe based SSD products easily and quickly.

Impletation

Applications

The core can be utilized in the controller of a variety of NVMe storage products:

- Standard NVMe SSD Controllers

- Application Specified NVMe Flash Cards

- NVMe products using other media types: PCM, RRAM, FeRAM, etc.

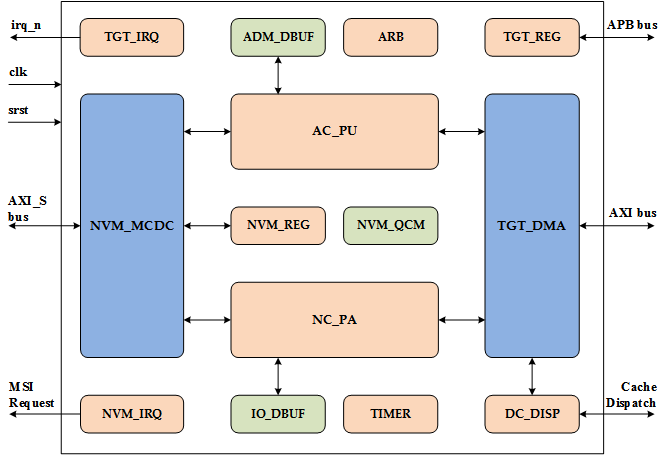

Block Diagram

The NVMe Target Core consists of two register modules, two DMA engines, two command process components, two interrupt generators, three memory buffers and one data cache dispatcher interface.

TGT_REG implements the core registers that can be accessed by the target CPU through AMBA APB bus. NVM_REG implements the NVMe protocol registers. TGT_DMA is a DMA engine that handles the data transfer with the target memory through AMBA AXI bus. NVM_MCDC is a multi-channel DMA controller that handles the data transfer with the host memory through AMBA AXI Stream bus. The AXI Stream bus connects to any of PCIe cores that provide an AXI Stream transmit interface and receive interface (e.g. Xilinx PCIe core). AC_PU processes Admin commands. NC_PA processed I/O commands in multiple threads. TGT_IRQ drives the interrupt line for the target CPU and NVM_IRQ module generates/manages the MSI requests for the PCIe core. ADM_DBUF and IO_DBUF buffers the intermediary data when processing Admin and NVMe commands respectively. NVM_QCM managers all Admin & I/O queue contexts. buffers all commands for one arbitration round processing. ARB implements the command arbitration logic and TIMER monitors the NVMe device power on hours and controller busy time.

DC_DISP module handles the data cache address request & management when NC_PA processes the I/O commands. It is flexible for the Core integrator to implement the outside connected cache dispatcher, which may be implemented mainly by software or a sophisticated hardware, perhaps depending on the target CPU performance and the application requirements.

Features

- Synchronoused design

- Compliant to NVMe 1.3c

- Configurable queue pairs and queue depths

- Supports WRR with urgent priority class arbitration mechanism

- Supports parallel I/O command process

- Automated PCIe MSI interrupt on posting of completions

- Provides AMBA APB register bus interface for the target CPU

- Provides AMBA AXI bus master interface for the target system memory

- Provides interrupt line for the target CPU

Standard Interface

Sales E-mail: sale@bjbytech.com

Technical consult E-mail: tech@bjbytech.com

Cell Phone: +8613601005061

Support

The core as delivered is warranted against defects for three months from purchase. Free remote technical support is provided for twelve months, includes consultation via phone and E-mail. The maximum time for processing a request for technical support is three business days.

Verification

The core has been verified through extensive simulation and rigorous code coverage measurements.

Deliverables

The core is available in RTL source code (Verilog) and FPGA (Netlist) forms, and includes everything required for successful implementation:

- RTL source code or post-synthesis EDIF Netlist (FPGAs)

- Wrapper for pin compatible replacement

- Testbench (self-checking)

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications