IP核库

- PCIe控制器

- NVMe控制器

- 闪存纠错码

- 闪存控制器

- HINOC2.0前向纠错码

授权优势:

- 可提供具体FPGA芯片(DNA ID)的网表

- 可提供具体FPGA型号的网表

- 可提供Verilog RTL源代码

- 特定型号的网表,RTL源代码无数量限制,免版权费

- 提供长达一年的技术支持

- 提供FPGA评估网表:单一ID,使用时间/次数受限

- 全球服务

最新新闻 & 事件

更多新闻2024年1月12日 北京博原科技有限公司发布初版PCIe 3.0 控制器 IP核 v3.10

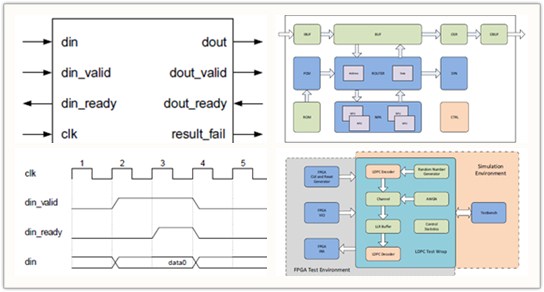

PCIe 3.0 控制器 IP核 v3.10支持:

符合PCIe 3.0协议规范。

链路宽度支持3种配置:x1,x2,x4, x8。

支持Root port,End Point。

支持最大负载: 128B,256B,512B,1024B。

用户接口:全双工模式,4路独立和AXI Stream接口。

链路层采用独有的重发算法,使得TX Buffer和Replay Buffer复用。

双时钟设计,链路层LCRC运行在用户时钟域uclk(不高于pclk频率),更易获得时钟收敛。

集成AXI Memory Mapped Bridge(可选功能)。

提供Xilinx PHY集成支持服务(Ultra系列 & Ultra+系列, 可选)。

提供Xilinx PHY集成支持服务(7系列,可选):集成第三方128b/130b软PCS后可允许在8.0GT/s。

2021年12月30日 北京博原科技有限公司发布新版NVMe Host IP核-AMBA v21.10

博原科技的NVMe Host IP-AMBA v21.10更新提示:

采用优化的TLP组包/拆包引擎,提升I/O性能。

原生支持RAID0,使得RAID0 IP更易被组建。

支持博原科技“PCIe控制器IP核”。

支持内核直接调用模式:寄存器控制接口,FIFO/RAM数据接口。

支持硬RAID0/1/5(可选)。

2021年12月20日 北京博原科技有限公司发布初版PCIe 2.0 控制器 IP核 v21.00

PCIe 2.0 控制器 IP核 v21.00支持:

符合PCIe 2.0协议规范。

链路宽度支持3种配置:x1,x2,x4。

支持Root port,End Point。

支持最大负载: 128B,256B,512B。

用户接口:全双工模式,4路独立和AXI Stream接口。

链路层采用独有的重发算法,使得TX Buffer和Replay Buffer复用。

双时钟设计,链路层LCRC运行在用户时钟域uclk(不高于pclk频率),更易获得时钟收敛。

支持数据链路层直连模式,允许用户自定义传输层。

提供Xilinx PHY集成支持服务(7系列,Ultra系列 & Ultra+系列, 可选)。